Susanta Ghosh (ICC-DataS/MEEM/MuSTI) is Principal Investigator on a project that has received a $170,604 research and development grant from the National Science Foundation. The project is titled “EAGER: An Atomistic-Continuum Formulation for the Mechanics of Monolayer Transition Metal Dichalcogenides.” This is a potential 19-month project.

Dr. Ghosh is an assistant professor of Mechanical Engineering-Engineering Mechanics at Michigan Tech. Before joining the Michigan Tech College pof Engineering, Dr. Ghosh was an associate in research in the Pratt School of Engineering at Duke University; a postdoctoral scholar in the departments of Aerospace Engineering and Materials Science & Engineering at the University of Michigan, Ann Arbor; and a research fellow at the Technical University of Catalunya, Barcelona, Spain. His M.S. and Ph.D. degrees are from the Indian Institute of Science (IISc), Bangalore. His research interests include multi-scale solid mechanics, atomistic modeling, ultrasound elastography, and inverse problem and computational science.

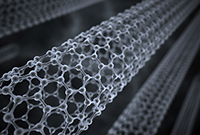

Abstract: Two-dimensional materials are made of chemical elements or compounds of elements while maintaining a single atomic layer crystalline structure. Two-dimensional materials, especially Transition Metal Dichalcogenides (TMDs), have shown tremendous promise to be transformed into advanced material systems and devices, e.g., field-effect transistors, solar cells, photodetectors, fuel cells, sensors, and transparent flexible displays. To achieve broader use of TMDs across cutting-edge applications, complex deformations for large-area TMDs must be better understood. Large-area TMDs can be simulated and analyzed through predictive modeling, a capability that is currently lacking. This EArly-concept Grant for Exploratory Research (EAGER) award supports fundamental research that overcomes current challenges in large-scale atomistic modeling to obtain an efficient but reliable continuum model for single-layer TMDs containing billions of atoms. The model will be translational and will contribute towards the development of a wide range of applications in the nanotechnology, electronics, and alternative energy industries. The award will further support development of an advanced graduate-level course on multiscale modeling and organization of symposia in two international conferences on mechanics of two-dimensional materials. Experimental samples of TMDs contain billions of atoms and hence are inaccessible to the state-of-the-art molecular dynamics simulations. Moreover, existing crystal elastic models for surfaces cannot be applied to multi-atom thick 2D TMDs due to the presence of interatomic bonds across the atomic surfaces. The crystal elastic model aims to solve this problem by projecting all interatomic bonds onto the mid-surface to track their deformations. The actual deformed bonds will, therefore, be computed using the deformations of the mid-surface. Additionally, a technique will be derived to incorporate the effects of curvature and stretching of TMDs on their interactions with substrates. The model will be exercised to generate insights into the mechanical instabilities and the role of substrate interactions on them. The coarse-grained model will overcome the computational bottleneck of molecular dynamics models to simulate TMDs samples comprising billions of atoms. This award reflects NSF’s statutory mission and has been deemed worthy of support through evaluation using the Foundation’s intellectual merit and broader impacts review criteria.

Mari W. Buche (DataS/SBE) attended the HERS Institute July 8-20, at Bryn Mawr College, Pennsylvania, Along with 63 women from a variety of colleges and universities across the country, Buche participated in professional development sessions focused on fine-tuning leadership skills unique to higher education. Visit

Mari W. Buche (DataS/SBE) attended the HERS Institute July 8-20, at Bryn Mawr College, Pennsylvania, Along with 63 women from a variety of colleges and universities across the country, Buche participated in professional development sessions focused on fine-tuning leadership skills unique to higher education. Visit  Bo Chen

Bo Chen

Researcher:

Researcher:  Researchers:

Researchers: Researcher:

Researcher:  Researcher:

Researcher: