Researcher: Shiyan Hu, PI, Adjunct Professor, Electrical and Computer Engineering

Researcher: Shiyan Hu, PI, Adjunct Professor, Electrical and Computer Engineering

Sponsor: National Science Foundation

Amount of Support: $222,315

Duration of Support: 4 years

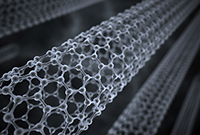

Abstract: This CAREER proposal aims to develop innovative chip layout design and optimization methodologies on nanotechnology interconnect and copper interconnect co-design. As the copper interconnect technology is approaching its fundamental physical limit, novel on-chip interconnect materials such as carbon nanotubes and graphene nano-ribbons have emerged as promising replacement materials due to properties such as superior conductivity and resilience to electromigration that otherwise have plagued copper interconnects. On the other hand, there could also be some issues for using nanotechnology interconnects such as their inferior performance as local interconnect and defects in fabrication. The PI will develop a novel co-design methodology which judiciously integrates nanotechnology into the practical VLSI circuit design together with various enabling techniques on co-design-aware buffering, layer assignment, routing, placement and clocking. The PI also proposes defect-aware techniques for mitigating the impacts due to defects, and improving robustness against faults for nanotechnology interconnects.

The broader impact of the proposed research is to significantly improve the circuit performance of nanoscale circuits. As the interconnect delay is the dominating factor of the circuit delay, the proposed research has the potential to help achieve the design closure for those difficult circuits whose timing cannot be closed even if various traditional physical synthesis optimizations have been stretched to the maximum extent. The proposed research can contribute integrated circuit design methodologies which enable the utilization of nanotechnologies into practical circuit design to defeat the fundamental limit on the prevailing VLSI technology. The PI will also develop a seamless integration of research with education such as developing the new graduate level course, developing lecture series and seminars, recruiting under-represented students, and showcasing the research results at conferences.

Publications:

Chen Wang, Li Jiang, Shiyan Hu, Tianjian Li, Xiaoyao Liang, Naifeng Jing, and Weikang Qian. “Timing-Driven Placement for Carbon Nanotube Circuits,” in Proceedings of IEEE International System-on-Chip Conference (SOCC), 2015, 2015.

Lin Liu, Yuchen Zhou and Shiyan Hu. “Buffering Carbon Nanotube Interconnects for Timing Optimization,” in Proceedings of IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 2014.

Jia Wang, Lin Liu, Yuchen Zhou, and Shiyan Hu. “Buffering Carbon Nanotube Interconnects Considering Inductive Effects,” Journal of Circuits, Systems and Computers (JCSC), v.25, 2016.

Yang Liu, Lin Liu, Yuchen Zhou, and Shiyan Hu. “Leveraging Carbon Nanotube Technologies in Developing Physically Unclonable Function for Cyber-Physical System Authentication,” in Proceedings of IEEE INFOCOM Cyber-Physical System Security Workshop, 2016.

Jacob Wurm, Yier Jin, Yang Liu, Shiyan Hu, Kenneth Heffner, Fahim Rahman, Mark Tehranipoor. “Introduction to Cyber-Physical System Security: A Cross-Layer Perspective,” IEEE Transactions on Multi-Scale Computing Systems, v.3, 2017, p. 215-227.

Researchers:

Researchers: Researcher:

Researcher:  Researcher:

Researcher:

Researcher:

Researcher:  Researchers:

Researchers: